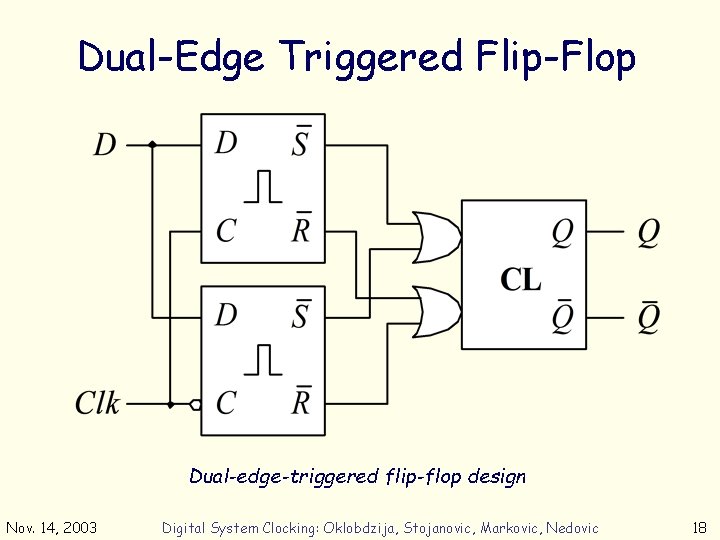

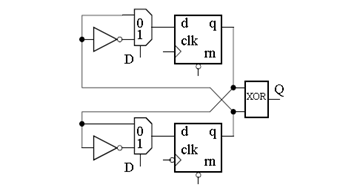

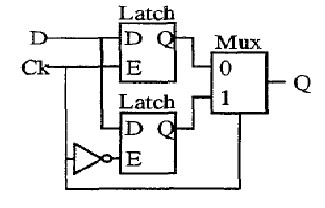

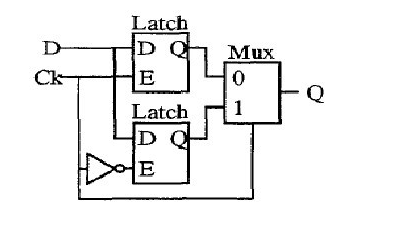

Dual edge-triggered static pulsed flip-flop (DSPFF): (a) dual pulse... | Download Scientific Diagram

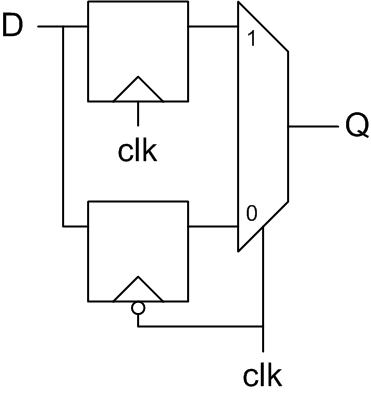

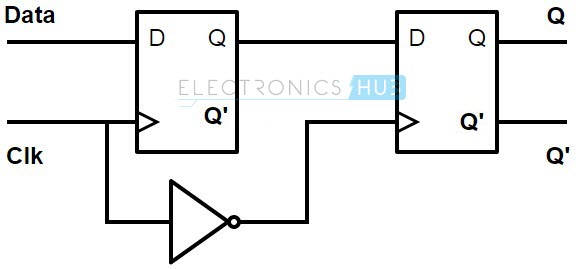

Dual edge sequential architecture capable of eliminating complete hold requirement from the test path

Dual edge sequential architecture capable of eliminating complete hold requirement from the test path